|

Frequency

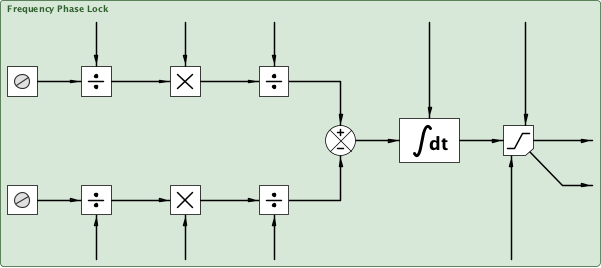

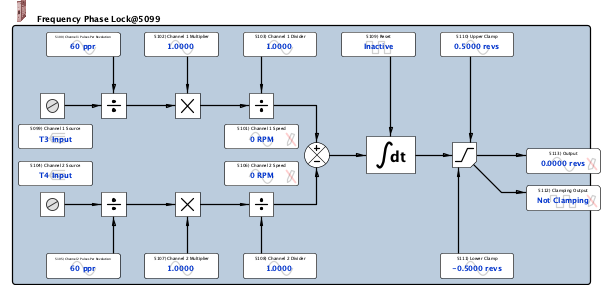

Frequency Phase Lock

|

| Description | (description coming soon) |

| Availability |

|

| savvy-SFD Graphic |  |

| Graphic with Parameters |  |

| Channel 1 Source |

Internal Parameter, Read-write, Enumerated (signed 16-bit integer) 0 = T3 Input 1 = T4 Input 2 = T5 I/O |

| Channel 1 Pulses Per Revolution |

Input, Read-write, Analog (signed 16-bit integer) 1 ppr to 30000 ppr |

| Channel 1 Speed |

Internal Parameter, Read-only, Analog (signed 16-bit integer) -32767 RPM to 32767 RPM |

| Channel 1 Multiplier |

Input, Read-write, Analog (signed 16-bit integer) -3.2767 to 3.2767 |

| Channel 1 Divider |

Input, Read-write, Analog (signed 16-bit integer) 0.0001 to 3.2767 |

| Channel 2 Source |

Internal Parameter, Read-write, Enumerated (signed 16-bit integer) 0 = T3 Input 1 = T4 Input 2 = T5 I/O |

| Channel 2 Pulses Per Revolution |

Input, Read-write, Analog (signed 16-bit integer) 1 ppr to 30000 ppr |

| Channel 2 Speed |

Internal Parameter, Read-only, Analog (signed 16-bit integer) -32767 RPM to 32767 RPM |

| Channel 2 Multiplier |

Input, Read-write, Analog (signed 16-bit integer) -3.2767 to 3.2767 |

| Channel 2 Divider |

Input, Read-write, Analog (signed 16-bit integer) 0.0001 to 3.2767 |

| Reset |

Input, Read-write, Boolean (signed 16-bit integer) 0 = Inactive 1 = Reset |

| Upper Clamp |

Input, Read-write, Analog (signed 16-bit integer) 0.0000 revs to 3.2767 revs If the Input exceeds this value, the Output will be set to this value. |

| Lower Clamp |

Input, Read-write, Analog (signed 16-bit integer) -3.2767 revs to 0.0000 revs If the Input is less than this value, the Output will be set to this value. |

| Clamping Output |

Output, Read-only, Boolean (signed 16-bit integer) 0 = Not Clamping 1 = Clamping |

| Output |

Output, Read-only, Analog (signed 16-bit integer) -3.2767 revs to 3.2767 revs -32767 = - overrange 32767 = + overrange |