|

Latches

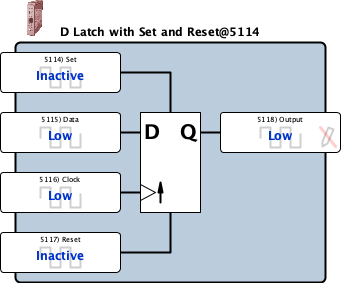

D Latch with Set and Reset

|

| Description | If the Set and Reset are both inactive and the Output value is the opposite value of the input Data, a rising edge of the Clock will change the Output to match the input Data. When the Reset is Enabled, the Output is forced LOW. When the Set is Enabled, the Output is forced HIGH. Order of Precedence: Reset => Set => Clock (rising) When the Data and Output are already the same values, a rising edge on the Clock will have no effect. The Output is not persistent when powered-down. |

| Availability |

|

| savvy-SFD Graphic |  |

| Graphic with Parameters |  |

| Set |

Input, Read-write, Set to default on hard initialization, Boolean (signed 16-bit integer) 0 = Inactive 1 = Set |

| Data |

Input, Read-write, Boolean (signed 16-bit integer) 0 = Low 1 = High |

| Clock |

Input, Read-write, Boolean (signed 16-bit integer) 0 = Low 1 = High |

| Reset |

Input, Read-write, Boolean (signed 16-bit integer) 0 = Inactive 1 = Reset |

| Output |

Output, Read-only, Set to default on hard initialization, Boolean (signed 16-bit integer) 0 = Low 1 = High |